### Programming Abstractions and Synthesis-Aided Compilation for Emerging Computing Platforms

by

Phitchaya Phothilimthana

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Rastislav Bodik, Co-chair Professor Katherine Yelick, Co-chair Professor David Culler Assistant Professor Zachary Pardos

Fall 2018

# Programming Abstractions and Synthesis-Aided Compilation for Emerging Computing Platforms

Copyright 2018 by Phitchaya Phothilimthana

#### Abstract

Programming Abstractions and Synthesis-Aided Compilation for Emerging Computing Platforms

bv

Phitchaya Phothilimthana

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Rastislav Bodik, Co-chair

Professor Katherine Yelick, Co-chair

Today's cutting-edge applications, ranging from wearable devices and embedded medical sensors to high-performance data centers, put new demands on computer architectures. Those demands include more computation capability, a tight power budget, low latency, high throughput, and many more. To meet these requirements, specialized architectures with low energy consumption are becoming more prevalent. Many of these architectures trade off programmability features for gains in energy efficiency and performance. Hence, programmability challenges are inevitable as applications continue to evolve and make new demands on computing architectures.

I propose key principles for improving programmability intended for application writers as well as compiler developers and language designers. First, I address programmability issues by providing a programming model that hides low-level details but sufficiently exposes essential details for application writers to control. Second, to compile and optimize programs, I apply a new compilation methodology based on synthesis. Unlike a classical compiler's transformation, synthesis obtains a correct and optimal solution by searching for an optimal candidate that is semantically equivalent to a specification program. This search helps compilers generate efficient code without deriving a program via a sequence of transformations, which are challenging for compiler developers to design for new unconventional architectures.

In this thesis, I demonstrate the key principles in three projects: Chlorophyll, a language and compiler for low-power spatial architectures; Floem, a programming system for NIC-accelerated data center applications; and GreenThumb, a framework for building a superoptimizer (an assembly program optimizer based on synthesis).

To my family.

### Contents

| Contents |                                                |                                              | ii            |

|----------|------------------------------------------------|----------------------------------------------|---------------|

| Li       | st of                                          | Figures                                      | iv            |

| Li       | st of                                          | Tables                                       | vii           |

| 1        | Intr<br>1.1                                    | roduction Programmability Challenges         | <b>1</b><br>1 |

|          | 1.2                                            | Compilation Approaches                       | 3             |

|          | 1.3                                            | Thesis and Goals                             | 5             |

|          | 1.4                                            | Concept I: Programming Model                 | 6             |

|          | 1.5                                            | Concept II: Synthesis-Aided Compilation      | 7             |

|          | 1.6                                            | Summary of Contributions                     | 10            |

| 2        | Chlorophyll: Programming Spatial Architectures |                                              | 11            |

|          | 2.1                                            | Contributions and Rationale                  | 12            |

|          | 2.2                                            | Overview                                     | 13            |

|          | 2.3                                            | Programming Model for Partitioning           | 14            |

|          | 2.4                                            | Synthesis-Aided Compiler                     | 28            |

|          | 2.5                                            | Toolchain and Debugger                       | 43            |

|          | 2.6                                            | Evaluation                                   | 44            |

|          | 2.7                                            | Extensive Case Study                         | 51            |

|          | 2.8                                            | Related Work                                 | 56            |

|          | 2.9                                            | Conclusion                                   | 59            |

| 3        | Flo                                            | em: Programming NIC-Accelerated Applications | 60            |

|          | 3.1                                            | Contributions                                | 60            |

|          | 3.2                                            | Design Goals and Rationale                   | 62            |

|          | 3.3                                            | Core Abstractions                            | 64            |

|          | 3.4                                            | Advanced Abstractions                        | 67            |

|          | 3.5                                            | Compiler                                     | 71            |

|          | 3.6                                            | PCIe I/O Communication                       | 75            |

|              | 3.7<br>3.8<br>3.9<br>3.10  | Evaluation                                  | 87<br>95<br>96<br>97 |

|--------------|----------------------------|---------------------------------------------|----------------------|

| 4            | $\operatorname{Gre}$       | enThumb: Superoptimization Framework        | 98                   |

|              | 4.1                        | Motivation                                  | 98                   |

|              | 4.2                        | Contributions                               | 99                   |

|              | 4.3                        | Overview of Search Strategy and Insights    | 100                  |

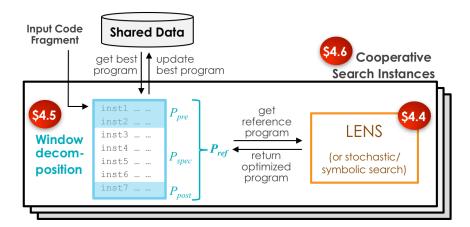

|              | 4.4                        | The Lens Algorithm                          | 106                  |

|              | 4.5                        | Context-Aware Window Decomposition          | 111                  |

|              | 4.6                        | Cooperative Superoptimizer                  | 112                  |

|              | 4.7                        | Superoptimization Construction Framework    | 114                  |

|              | 4.8                        | Evaluation                                  | 116                  |

|              | 4.9                        | Related Work                                | 124                  |

|              | 4.10                       | Conclusion                                  | 125                  |

| 5            | Tow                        | ard Resource-Mapping Framework              | 127                  |

|              | 5.1                        | Overview                                    | 127                  |

|              | 5.2                        | Library                                     | 127                  |

|              | 5.3                        | Case Study: Program Partitioning            | 129                  |

|              | 5.4                        | Future Work                                 | 133                  |

| 6            | Conclusion and Future Work |                                             |                      |

|              | 6.1                        | Trends in Emerging Computing Platforms      | 135                  |

|              | 6.2                        | Trends in Compilation                       | 135                  |

|              | 6.3                        | Lessons Learned and Thoughts for the Future | 136                  |

| Bibliography |                            |                                             | 138                  |

## List of Figures

| 0.1  | Bodik's research group in 2012–2018                                                                                                                                                                                                          | X     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.1  | Comparison of different compilation techniques                                                                                                                                                                                               | •     |

| 1.2  | Instantiation of the key concepts in the thesis, centering around exploiting an emerging computer architecture for performance and energy efficiency                                                                                         | Ę     |

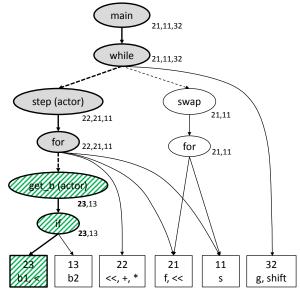

| 1.3  | Decomposition of the Chlorophyll compiler. Synthesis components are highlighted in blue                                                                                                                                                      | 8     |

| 2.1  | Example program written in Chlorophyll, and intermediate results from partitioning, layout, and code separation steps                                                                                                                        | 15    |

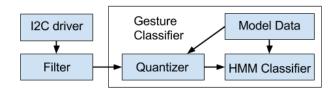

| 2.2  | A simplified example program taken from the gesture recognition application                                                                                                                                                                  | 21    |

| 2.3  | Program fragments of partitions 22, 23, and 13 generated by the compiler when compiling the program in Figure 2.2. The compiler places blue, pink, and purple highlighted data and computations from Figure 2.2(a) in partitions 22, 23, and |       |

|      | 13 respectively. N, S, E, and W stand for north, south, east, and west ports                                                                                                                                                                 | 22    |

| 2.4  | Typing rules                                                                                                                                                                                                                                 | 24    |

| 2.5  | Example of a parallel HMM classification program using the module construct .                                                                                                                                                                | 26    |

| 2.6  | Evaluation rules for an upper bound on the number of communications. $lut$ is                                                                                                                                                                |       |

|      | the function table. $lut[f] \leftarrow n$ is storing $n$ at index $f$ of the lookup table                                                                                                                                                    | 30    |

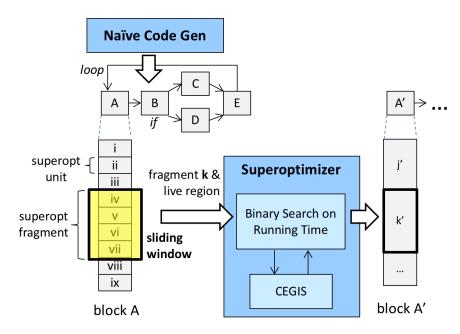

| 2.7  | Overview of the modular superoptimizer                                                                                                                                                                                                       | 38    |

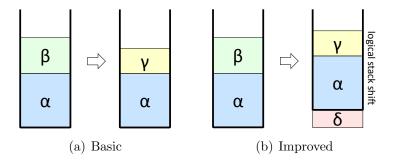

| 2.8  | Specification on data stack                                                                                                                                                                                                                  | 36    |

| 2.9  | Basic specification rejects an instruction sequence that leaves $a$ at the bottom of                                                                                                                                                         |       |

| 0.10 | the stack                                                                                                                                                                                                                                    | 36    |

| 2.10 | Execution time of multicore benchmarks normalized to program generated by the                                                                                                                                                                | 4.5   |

| o 11 | complete synthesizing compiler                                                                                                                                                                                                               | 45    |

|      | Single-core benchmarks                                                                                                                                                                                                                       | 47    |

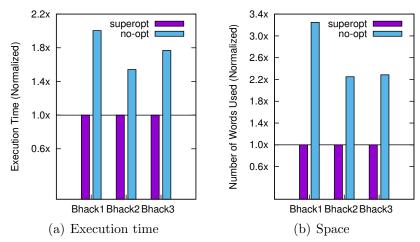

|      | Bithack benchmarks                                                                                                                                                                                                                           | 49    |

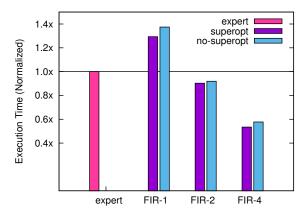

|      | FIR benchmark                                                                                                                                                                                                                                | 51    |

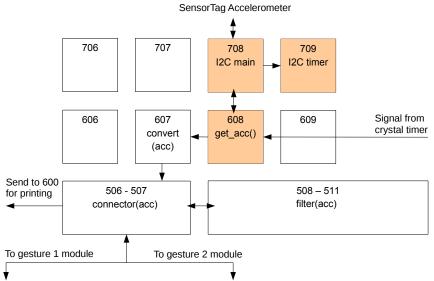

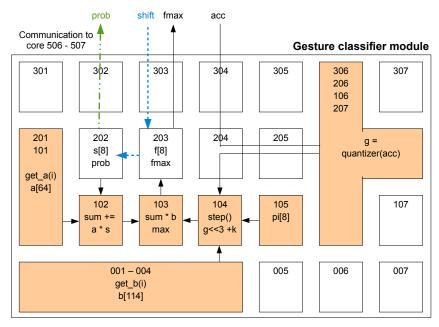

|      | Program layout for the gesture recognition application. Each core is labeled with                                                                                                                                                            | 91    |

| ۷.13 | three digits. The first digit indicates the x-coordinate. The last two digits indicate                                                                                                                                                       |       |

|      | the y-coordinate. Orange highlights cores that are actors                                                                                                                                                                                    | 52    |

|      | the y-coordinate. Orange inglinglis cores that are actors                                                                                                                                                                                    | $0^2$ |

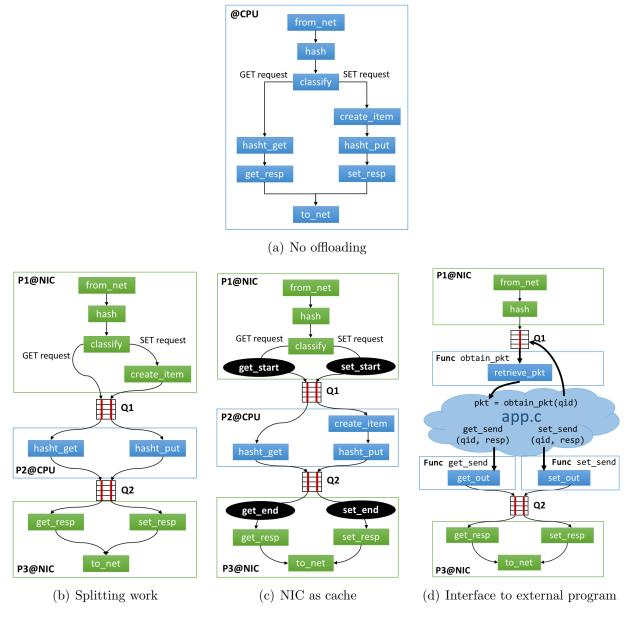

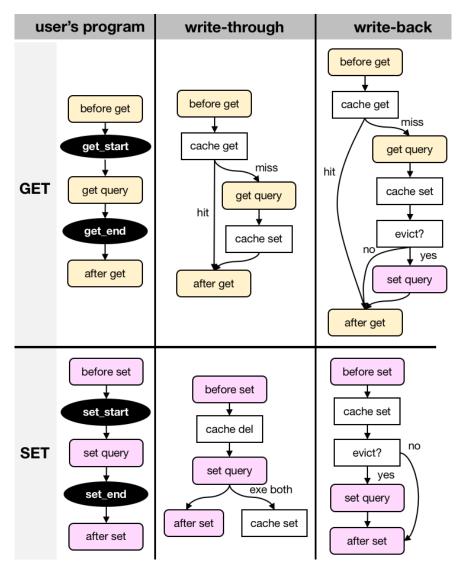

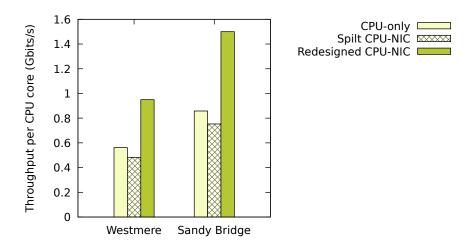

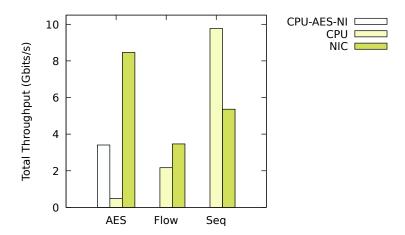

| 3.1<br>3.2   | Several offloading strategies of a key-value store implemented in Floem Floem program implementing a sharded key-value store with the CPU-NIC split strategy of Figure 3.1(b)                                                                                                                                          | 65<br>68   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

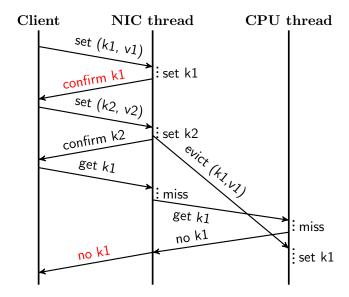

| 3.3          | Inconsistency of a write-back cache if messages from NIC to CPU are reordered                                                                                                                                                                                                                                          | 69         |

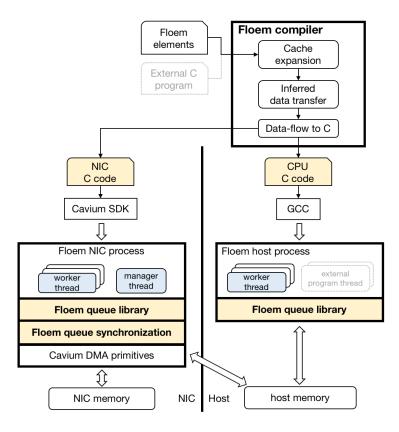

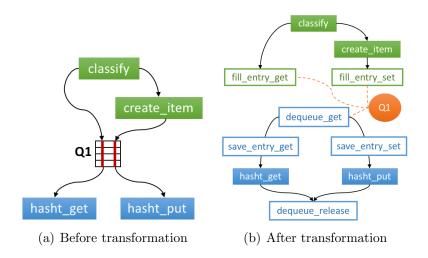

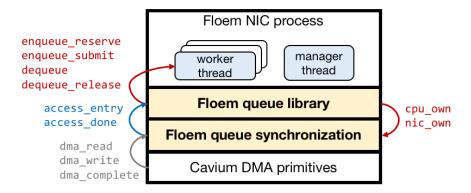

| 3.4<br>3.5   | FLOEM system architecture                                                                                                                                                                                                                                                                                              | 72<br>73   |

| 3.6          | split CPU-NIC version                                                                                                                                                                                                                                                                                                  | 74         |

| 3.7          | Provided API functions by different components. $A \xrightarrow{f} B$ represents: $A$ provides function $f$ for $B$ to use                                                                                                                                                                                             | 76         |

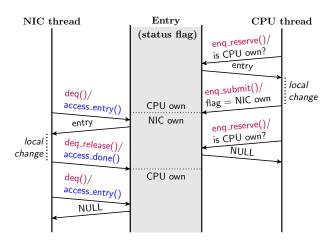

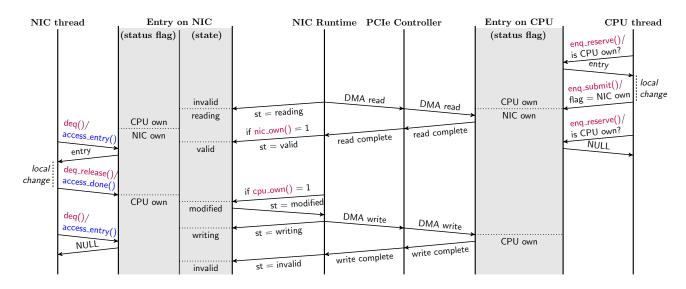

| 3.8          | Interaction between NIC runtime manager thread, NIC worker thread, CPU workder thread, and status of a queue entry. Red highlights functions provided by the queue library. Blue highlights functions provided by the queue synchronization layer. enq and deq are abbreviations for enqueue and dequeue respectively. | 70         |

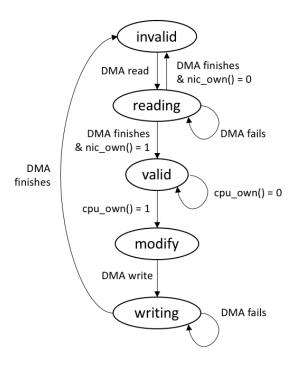

| 3.9          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                  | 78<br>79   |

| 3.10         | Example application pseudocode                                                                                                                                                                                                                                                                                         | 80         |

|              |                                                                                                                                                                                                                                                                                                                        | 81         |

| 3.11         | Pseudocode of the queue synchronization layer                                                                                                                                                                                                                                                                          | 85         |

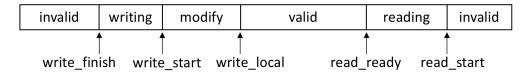

|              | States of different portions in a queue. Pointers always advance to the right and                                                                                                                                                                                                                                      | 69         |

| 3.14         | wrap around. Each portion contains zero or more queue entries. A timeline of a queue entry is depicted in Figure 3.8(b)                                                                                                                                                                                                | 85         |

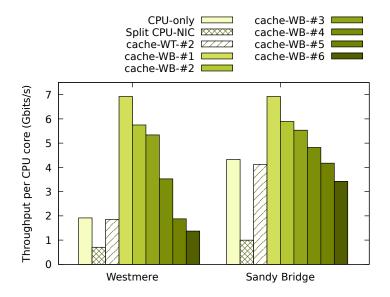

|              | uration number. Table 3.2 shows the cache sizes of the different configurations                                                                                                                                                                                                                                        |            |

|              | and their resulting hit rates                                                                                                                                                                                                                                                                                          | 88         |

| 3.15<br>3.16 |                                                                                                                                                                                                                                                                                                                        | 91         |

| 3 17         | running on one CPU core with AES-NI                                                                                                                                                                                                                                                                                    | 92         |

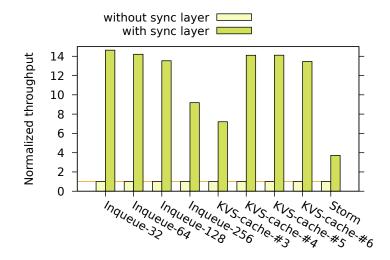

| 0.11         | without the sync layer                                                                                                                                                                                                                                                                                                 | 94         |

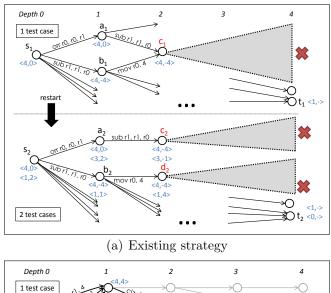

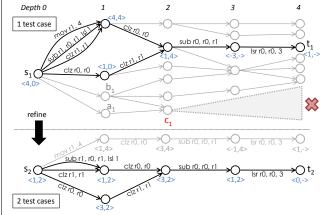

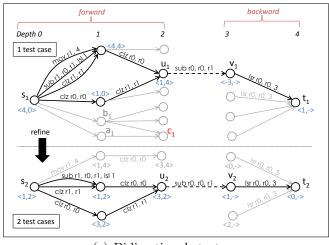

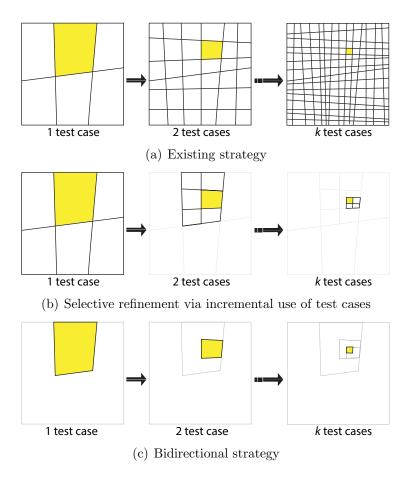

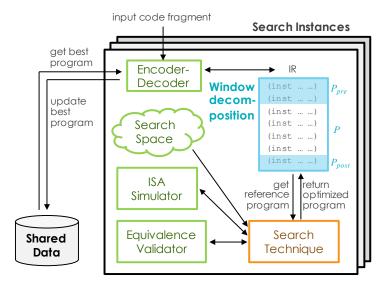

| 4.1<br>4.2   | Interaction between the main components in our superoptimizer Search graphs of ARM programs of length 4. In (b) and (c), the highlighted paths are programs that pass the test cases. Assume programs are executed on 4-bit                                                                                            | 101        |

| 4.3          |                                                                                                                                                                                                                                                                                                                        | 102        |

| 4.4          | equivalence classes                                                                                                                                                                                                                                                                                                    | 103        |

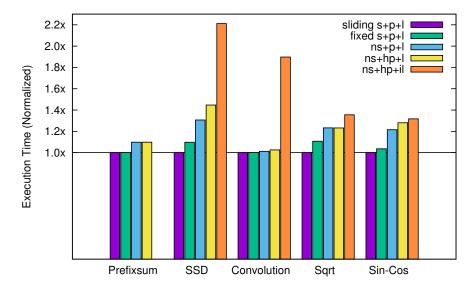

| 4.5          | 1 0                                                                                                                                                                                                                                                                                                                    | 105<br>114 |

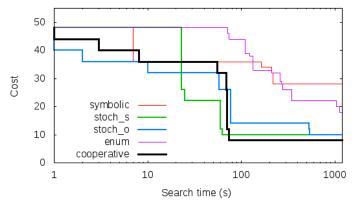

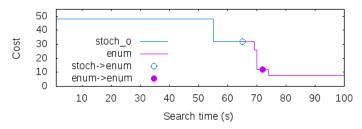

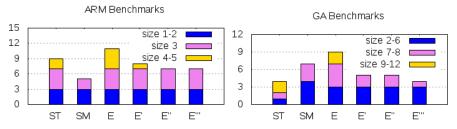

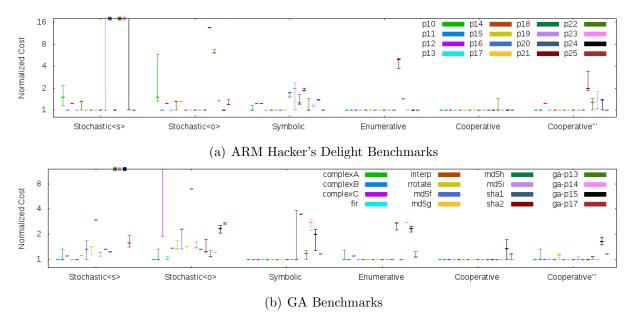

| 4.6 | Comparing base search techniques                                                     | 118 |

|-----|--------------------------------------------------------------------------------------|-----|

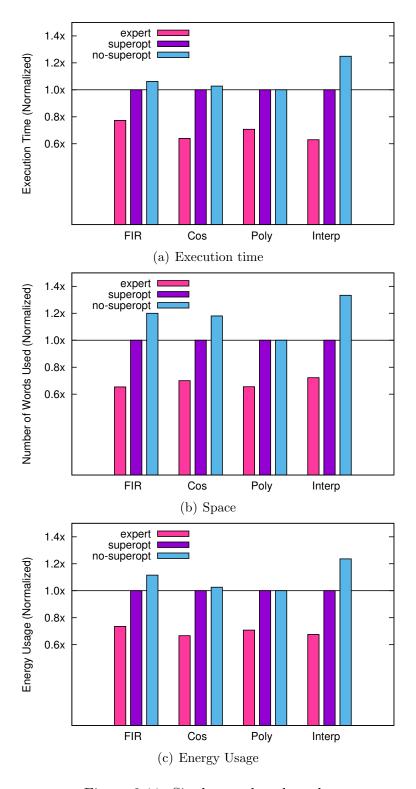

| 4.7 | Costs of best programs found by the different superoptimizers (normalized by         |     |

|     | the cost of the best known program). A dash represents the cost of the best          |     |

|     | program found in one run. A dash may represent more than one run if the best         |     |

|     | programs found in different runs have the same cost. If one or two runs did not      |     |

|     | find any correct program that is better than the input program, the vertical line    |     |

|     | is extended past the chart. If none of the runs found a correct program that is      |     |

|     | better than the input program, a <b>rectangle</b> is placed at the top of the chart. | 120 |

| 4.8 | Optimizations that the cooperative superoptimizer discovered when optimizing         |     |

|     | mi-bitarray benchmark. Blue highlights the difference between before and after       |     |

|     | each optimization. (a) is the original program. (b) is the intermediate program.     |     |

|     | (c) is the final optimized program. $\dots$                                          | 123 |

| 5.1 | Original type checker, ensuring that code fragments fit into cores                   | 130 |

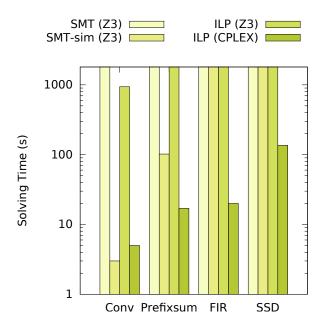

| 5.2 | Type checker in resource language, producing ILP constraints                         | 130 |

| 5.3 | Running example of program partitioning                                              | 131 |

| 5.4 | Symbolic expression of space occupied in each core after running a type checker      |     |

|     | on the yellow nodes in the example AST (Figure 5.3(a))                               | 131 |

| 5.5 | Time to solve program partitioning                                                   | 132 |

### List of Tables

| 2.1 | Superoptimization time (in hours) and program length (in words) for single-core benchmarks. A word in program sequences contains either four instructions or a constant literal. *Bithack-3 takes 25.08 hours when the program fragment length is capped at 30 instructions. With the default length (16 instructions), it takes |          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2 | 2.5 hours                                                                                                                                                                                                                                                                                                                        | 50<br>50 |

| 2.3 | Total execution time and energy consumption per one round of classification                                                                                                                                                                                                                                                      | 55       |

| 2.4 | Energy consumption per each task per one round of classification                                                                                                                                                                                                                                                                 | 55       |

| 2.5 | Size of generated code. Each core can store up to 64 words of data and program.                                                                                                                                                                                                                                                  | 56       |

|     |                                                                                                                                                                                                                                                                                                                                  |          |

| 3.1 | Effort to implement key-value store. The last column describes specific modification details other than creating, modifying, and rewiring elements. As a baseline, code relevant to communication on the CPU side alone was 240 lines in a manual                                                                                |          |

| 3.2 | C implementation                                                                                                                                                                                                                                                                                                                 | 88       |

|     | for write-through. $\infty$ entries mean a linked list                                                                                                                                                                                                                                                                           | 89       |

| 3.3 | Effort to implement Storm. The last column describes specific modification de-                                                                                                                                                                                                                                                   |          |

|     | tails other than creating, modifying, and rewiring elements                                                                                                                                                                                                                                                                      | 91       |

| 3.4 | Speedup when sending only the live portions when varying live ratios from a                                                                                                                                                                                                                                                      |          |

|     | micro-benchmark. Sizes are in bytes (B)                                                                                                                                                                                                                                                                                          | 94       |

| 4.1 | The differences between non-context-aware and context-aware decomposition. $p$ is a candidate program. $i_{ce}$ is the input counterexample returned by the constraint                                                                                                                                                           |          |

|     | solver if the candidate program is not equivalent to the reference program                                                                                                                                                                                                                                                       | 112      |

| 4.2 | Median time in seconds to reach best known programs. "-" indicates that the superoptimizer failed to find a best known program in one or more runs. Bold denotes the fastest superoptimizer to find a best known program in each benchmark                                       | 190 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3 | Execution time speedup over $gcc$ -03 code and search instances involved in finding the solution. In the last column, $X \to Y$ indicates that $Y$ uses the best code found by $X$ . * indicates exchanging of the best code among search instances of the same search technique |     |

| 5.1 | Description of resource language operations. Sym/conc stands for symbolic or concrete                                                                                                                                                                                            | 128 |

| 5.2 | Implementation of resource language operations. $sum^{\dagger}$ and $offset^{\dagger}$ are temporary variables                                                                                                                                                                   | 129 |

### Acknowledgments

I would like to give acknowledgments in chronological order through the journey of my life and this thesis.

I was born to the Phothilimthana family. I am eternally grateful for unconditional love from my parents and sister. I thank them for teaching me to always have faith in myself and believe that I can do whatever I wish and work toward. I thank them for raising me to be me today.

In 2004, I was introduced to programming in the required programming course during my first year of high school at Mahidol Wittayanusorn School. Mahidol Wittayanusorn School is the best high school in Thailand, in my opinion of course. I thank all my teachers and the school for taking me to the beginning of my exciting career path in computer science.

In 2006, I represented Thailand at International Olympiad in Informatics (IOI) and thus received a scholarship from the Thai government to study abroad. Thanks to all the organizers of the programming camps, especially to Jittat Fakcharoenphol, for making me discover the joy of solving programming problems through my path to IOI. I am grateful to the Thai government for giving me an amazing opportunity to study at the top university in the world.

In 2010, friends convinced me to take the 6.035 compiler class at MIT taught by Saman Amarasinghe. I later joined his research group. I never thought that I would ever take a compiler class, but I did only because of my friends, Yod Watanaprakornkul and Melissa Gymrek. I thank them for convincing me to take this class. Then, Saman asked me to join his research group after I took his class. I accepted this great offer, and I have been doing compiler research ever since. I would like to thank Saman for introducing me to compilers and research and for giving career advice. I also thank Jason Ansel, my graduate student mentor, who advised me through my first published project at MIT, and for all his support as my friend and husband.

In 2012, I met my Ph.D. advisor, Ras Bodik. I first met Ras during the visit days, and I instantly felt his enthusiasm and love in research. He introduced me to GreenArrays, my then future-to-be research project, even before I decided to join Berkeley. After working with Ras for six years, I can say that I could not have asked for a better advisor. Ras pushed me for the better, but at the same time cared for my well-being. Ras liked to ask for many revisions for that perfect presentation and paper's introduction and overview. He sometimes "twisted" my arm to make cool demos, like running applications using a lemon or potato battery! Although they were a lot more work than I signed up for, I am grateful for such

advice, which certainly made my work ten-times cooler and more exciting. I am genuinely thankful for all the guidance and lengthy discussions during our weekly meetings that always ran late.

Shortly, I joined the Berkeley Computer Science Ph.D. program. Apart from having a great advisor, I also had an awesome, supportive research group. Thanks to Leo Meyerovich, Joel Galenson, Thibaud Hottelier, Shaon Barman, Ali Koksal, Sarah Chasins, Julie Newcomb, Sam Elliott, Sam Kaufman, Chenglong Wang, and Rohin Shah. They showed me how to have fun and be happy in grad school. I enjoyed all our conversations over daily lunch from the co-op living situation to a serious grad school business. Special thanks to Sarah Chasins, my academic twin, who is the most caring and supportive grad student friend I have. As a token of appreciation, I dedicate the illustration in Figure 0.1 to the group. Also, many thanks to my sweet grad student fellows, Penporn Koanantakool and Neeraja Yadwadkar, for listening, sharing, and fun hangouts. Thanks to everyone in Chaperone, the Berkeley PL research lab.

In 2015, here came the surprise. Ras moved to the University of Washington, so I asked Kathy Yelick to be my co-advisor. I am grateful to Kathy for making sure I was doing okay when I worked remotely with Ras. I am also thankful for her feedback on writing and presentation for my qualifying examination and this thesis.

In 2016, I moved to the University of Washington as a visiting student. Shoutouts to PLSE and SAMPA labs for the fun and lively research environment at UW.

In 2018, my ultimate frisbee team got the third place from Masters Women's Nationals Championship. A big part of my grad student's life apart from research is playing ultimate frisbee. I am grateful to the ultimate frisbee community for the welcoming, inclusive environment and the fun breaks from research.

Finally, I filed this thesis. To all my collaborators, Emina Torlak, Tikhon Jelvis, Rohin Shah, Nishant Totla, Sarah Chasins, Michael Schuldt, Aditya Thakur, Dinakar Dhurjati, Ming Liu, Antoine Kaufmann, Simon Peter, Tom Anderson, Greg Bailey, Charley Shattuck, Per Ljung, Paulo Matos, and Vinod Grover, it has been a pleasure collaborating with you all. Thank you for making these projects in my thesis possible. Thanks to the rest of my dissertation committee members, David Culler and Zachary Pardos, for their insightful feedback and suggestions. Last but not least, I appreciate the help from the Berkeley ParLab and UW PLSE staff: Roxana Infante, Tamille Chouteau, Kostadin Ilov, Lydia Raya, and Amanda Robles.

Figure 0.1: Bodik's research group in 2012–2018

### Chapter 1

### Introduction

Leading-edge applications, ranging from smart devices to high-performance data centers, put new demands on computing hardware. These demands include more computation power, low energy consumption, high performance, etc. To meet these requirements after the end of Moore's law, specialized architectures with low power are becoming more popular. These architectures often sacrifice programmability features for gains in performance and energy efficiency. Hence, programmability challenges are unavoidable as applications evolve and make new demands on computing hardware.

### 1.1 Programmability Challenges

In this thesis, programmability challenges posed by recent emerging computer architectures are categorized into three kinds, as follows.

Challenges due to specialization. Specialized architectures force programmers to reason about their unconventional characteristics or control decisions that are not typically made by programmers, resulting in new programming challenges.

Specialized processors for low-power, energy-efficient applications often have minimalistic resources, such as narrow bitwidth, small memory, and simple interconnects. For example, TI MSP430 ultra-low-power MCUs, widely used microcontrollers, have 16-bit words and contain only up to 256 kilobytes of memory [75]. Atmel AVR, used in most Arduino boards, is even more extreme, using only 8 bits per word [15, 109]. GreenArrays GA144, a highly energy-efficient chip, has 300 bytes of memory per core and 18-bit words [65]. Narrow bitwidth introduces more overflow and precision problems, forcing programmers to carefully manipulate numbers in certain ways or use multiple words to represent a number that requires high precision. At the same time, programmers have to make their programs and data fit in tiny memory. Besides narrow bitwidth and small memory, some processors employ spatial designs that reduce energy consumption by requiring software-managed communication between computing elements with limited interconnects. GA144 has a simple 2D mesh inter-

connect of 144 asynchronous cores with no shared memory. This design allows a few small cores to be active at a time, thus, consuming very little power overall. Furthermore, the nonexistence of synchronized clock in GA144 is crucial to achieve ultra-low energy consumption [30]. However, the spatial design forces programmer to partition programs and data onto different locations (e.g., cores). This process is extremely challenging when each core is minuscule.

Specialized hardware developed for accelerating applications in a specific domain also exposes its own unique features. GPUs, originally designed for graphic computations, are now used for accelerating applications from various domains — such as scientific computing, data processing, and machine learning — thanks to its massive parallelism [110]. However, GPU programmers must coordinate a massive number of threads to work collaboratively in a SIMT style and manage scratchpad memory manually. Barefoot Tofino, a programmable Ethernet switch, exposes its match-action computing stages to users and forces them to program in a match-action programming paradigm [20]. The spatial design that is employed in processor design for energy efficiency can also be used for performance. Spatial architectures such as FPGAs and WaveFlow [45, 39] exploit data locality for low latency, and massive pipeline parallelism in data-flow computation for high throughput.

Challenges due to heterogeneity. Heterogeneous computing refers to systems that use more than one kind of processor [53, 110]. Heterogeneity in a system poses multiple new challenges to programmers. The first challenge is dividing the workload among different computing devices. This process is extremely difficult because programmers must understand the tradeoffs between running different kinds of computation on different devices as well as inter-device communication, which are expensive across devices. Second, after the programmers decide how to partition an application across multiple devices, they have to write multiple programs to run on those devices. Different hardware architectures often accept code written in different languages with different programming paradigms and require different optimization tricks. If the programmers change how they partition the application, they will need to modify programs running on all devices. Therefore, heterogeneous computing demands a huge effort from programmers in order to explore a variation of workload assignment.

Challenges due to performance understanding. New programming challenges also arise from complicated performance characteristics of interacting components in the hardware architectures. For example, GPU programmers must understand thread divergence, memory coalescing, shared memory bank conflicts, and register spill in order to achieve good performance on GPUs. Spatial architectures such as GA144, WaveFlow, and FPGAs expose highly-variable latency for instruction operands, depending on the spatial distance between the operands and the instructions. For heterogeneous computing, it is especially hard to estimate the performance of an implementation accurately. A static performance model is often imprecise because it abstracts away some complexity of the hardware model.

We can avoid a static approach by evaluating the performance of a task empirically, but we still cannot simply assign a placement of a task in isolation because it interacts with other parts of the application. Unfortunately, we often cannot afford to test all possible choices considering the entire application because the space is too big. Therefore, there has been a large body of work on automatically mapping a program to different hardware nodes [110], but there is still no solution for all.

This thesis primarily addresses the challenges due to specialization and heterogeneity. Some of the proposed methods, however, indirectly solve the last challenge by making it easier to explore many implementations of programs.

### 1.2 Compilation Approaches

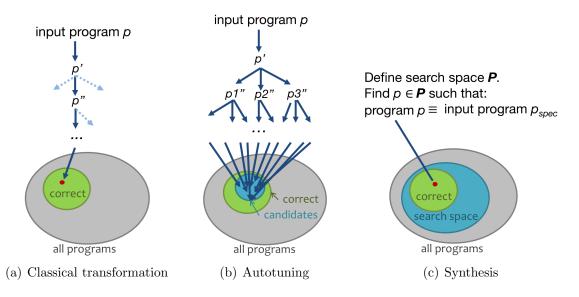

Programmability challenges can be solved by a programming model that has the right level of abstraction for an application domain, together with a compiler that can lower a higher-level program written by a programmer to executable code. To achieve good performance, the programmer relies on the compiler to generate efficient code. In this section, I compare and contrast different compilation techniques, and discuss their potential to solve the programmability challenges posed by emerging specialized architectures and their impacts on programming abstractions. Figure 1.1 summarizes how each approach produces an output code.

Classical compiler transformations. Researchers have studied compiler technology for over sixty years [9]. A set of program transformations allow programmers to write pro-

Figure 1.1: Comparison of different compilation techniques

grams in higher-level languages like Fortran instead of assembly. Many transformations have forever changed the way we program. Register allocation allows programmers to reason about virtual variables instead of physical registers. Instruction scheduling hides some low-level performance understanding from programmers. Compilers have become easier to build thanks to parser generators, analysis frameworks, and compiler infrastructures such as LLVM [89]. Nevertheless, building compilers in general, and especially those for new, unconventional processors, remains daunting. The classical approach to building compilers requires the laborious development of program analyses and transformations along with heuristics that select the best set of transformations and order them. As a result, building a mature new compiler may take a decade or more and require extremely high levels of professional expertise [131]. Furthermore, existing well-developed analyses and transformations may no longer be applicable to unconventional architectures, and hard-coded heuristic decisions that are tuned on a specific architecture often lead to suboptimal performance on other architectures.

Autotuning. One promising technology that addresses some programmability challenges due to performance understanding and heterogeneity is autotuning [12, 13, 55, 56, 119, 126, 129, 164]. Unlike classical compilers, autotuning compilers do not use fixed heuristics regarding how to apply different transformations. Instead, they try applying various semantics-preserved transformations with different parameters to obtain many correct output programs, run these programs, and select the one that performs best. Autotuning has been used to determine best configurations for long-running or frequently-executed applications to justify the time spent on tuning. While developers do not need to implement heuristics to select and order program transformations, they must still develop the transformations, a major challenge due to specialization in unconventional hardware.

Synthesis. Synthesis is an automatic code generation technique that has been rarely utilized in compilers. Synthesis obtains a correct and optimal solution by searching through a candidate space for an optimal candidate that is semantically equivalent to a specification program or satisfies some constraints [103, 147]. A candidate space typically includes both correct and incorrect candidates, for example, all instruction sequences of length up to 10. In contrast, a candidate space for autotuning typically includes only correct candidates. Synthesis typically employs a constraint solver, such as an SMT solver, to prove the correctness (e.g., being equivalent to a specification program) of an output solution and discard incorrect candidates. By searching the space by increasing length, one is guaranteed to eventually find a correct program (and probably one that is optimal).

The search among both correct and incorrect programs allows us to produce efficient code without deriving an input program through a sequence of semantics-preserved trans-

<sup>&</sup>lt;sup>1</sup>It is possible that autotuning search space may contain illegal candidates such as candidates that use more memory than available, but a percentage of illegal candidates is much smaller than that in synthesis search space.

formations, which are challenging for compiler developers to design and implement. More importantly, fast and correct implementations will be missed by a transformation-based compiler if the compiler developers do not include transformations required to produce the desired output. Thus, synthesis is more promising than the other approaches for solving programmability challenges due to specialization of unconventional architectures.

However, a major limitation of this approach is its speed and scalability to solve larger programs, similar to autotuning. This limitation is more pronounced in the synthesis setting because a search space of synthesis typically contains many incorrect candidates, much more than correct ones. If a search space is too big, we may not even discover any correct candidate. Therefore, synthesis has not been used as part of the main workflow of a compiler.

### 1.3 Thesis and Goals

This thesis primarily addresses the programmability challenges due to specialization and heterogeneity of unconventional emerging computing platforms. The main goal of this thesis is to enable programmability on new hardware architectures for gains in energy efficiency and/or performance of applications. My approach toward this goal advocates the following key concepts for designing and developing programming systems for emerging computing platforms.

- Concept I: design a programming model with a division of responsibilities between programmers and different components in a compiler.

- Concept II: apply synthesis in a compiler to sidestep hard-to-develop program transformations.

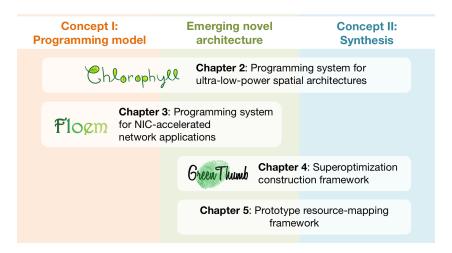

Figure 1.2: Instantiation of the key concepts in the thesis, centering around exploiting an emerging computer architecture for performance and energy efficiency.

Figure 1.2 summarizes the instantiation of these concepts in the chapters throughout this thesis, centering around exploiting an emerging novel computer architecture for performance and energy efficiency.

### 1.4 Concept I: Programming Model

We must design a programming model in a way that the responsibilities are divided judiciously among compiler's components (e.g., classical transformations, autotuners, and synthesizers), as well as programmers to achieve the most efficiency and/or performance. The philosophy behind this concept is that different components of the system, including humans, are good at different tasks. For example, human experts are often still better than machines on designing algorithms and data structures. Programmers may also relax semantics of a program to explore a new design without compromising the correctness of the program, while a compiler is unable to do this.

Hence, a programming model should strike a balance between hiding low-level details that can be solved efficiently by a compiler from programmers and exposing important details that programmers can control when the details are more suitable for humans to solve. This balance will ultimately let programmers productively explore various implementation choices to choose the best one. I demonstrate in this thesis how to apply this concept when designing the programming models for (1) Chlorophyll, a programming system for low-power embedded applications and (2) Floem, a programming system for NIC-accelerated network applications.

Chlorophyll (Chapter 2). I introduce a programming system for ultra-low-power spatial architectures. The system can generate code for GreenArrays GA144 [65], an energy-efficient, 144-core tile processor with distributed memory and simple interconnect. GA144 has very tiny per-core memory and uses stacks instead of registers.

The Chlorophyll programming model lets programmers provide their insights into how to partition data structures and code for the parts they choose since humans are more skilled than compilers in designing high-level program layouts. Chlorophyll mitigates programability challenges due to idiosyncratic characteristics of GA144 by letting the compiler handle the rest of programming partitioning, layout, data routing, and code generation for stack-based instructions. We use Chlorophyll to implement an accelerometer-based, hand-gesture recognition application for GA144. Compared to MSP430, GA144 is 19 times more energy efficient and 23 times faster when running this application. As a result, this application can run on a GA144 powered by a single potato!

Floem (Chapter 3). I introduce a programming system for NIC-accelerated network applications, balancing the ease of developing a correct application and the ability to refactor it to explore different design choices in a combined CPU-NIC environment.

FLOEM mitigates programmability challenges due to system heterogeneity and specialization of emerging programmable NICs through convenient program constructs. FLOEM enables offload design exploration by providing programming abstractions to assign computation to hardware resources; control mapping of logical queues to physical queues; access fields of a packet and its metadata without manually marshaling a packet; use a NIC to memoize expensive computation; and interface with an external application. The compiler infers which data must be transferred between the CPU and NIC and generates a complete cache implementation, while the runtime transparently optimizes DMA throughput. I use FLOEM to explore NIC-offloading designs of real-world applications, including a key-value store and a distributed real-time data analytics system; improve their throughput by 1.3–3.6× and by 75–96%, respectively, over a CPU-only implementation.

### 1.5 Concept II: Synthesis-Aided Compilation

Synthesis searches through a candidate space for an optimal candidate that is semantically equivalent to a specification program or satisfies some constraints. I envision synthesis as a means to enable a compiler to solve more sophisticated problems and discover better solutions, bridging increasingly larger gaps between high-level programming abstractions and actual hardware instructions. Additionally, synthesis is also a low-effort approach to compiler construction, lessening a compiler's development time while still generating code that is comparable in quality to code written by an expert or generated by a classical optimizing compiler. This is because synthesis sidesteps the need to develop program transformations, which are difficult to design and realize [101, 131], mitigating programmability challenges due to specialization from compiler developers. Furthermore, synthesis-aided compilation is more robust than transformation-based compilation because synthesis does not rely on pattern-matching using pre-defined rules.

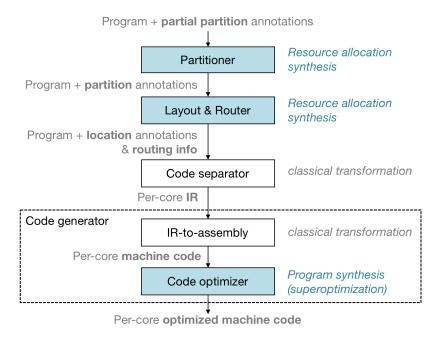

In Chlorophyll (Chapter 2), I phrase the partitioning, layout, and routing as synthesis problems because heuristic algorithms often fail to discover optimal solutions [14, 59, 114, 168]. Code generation uses a classical transformation that translates intermediate representations (IRs) to assembly. This transformation is straightforward to develop because it contains no optimization. After the IR-to-assembly transformation, I apply superoptimization (instruction-level synthesis) to perform local, machine-specific optimizations, without developing any semantics-preserved transformation. The compilation steps are summarized in Figure 1.3. Programs generated by Chlorophyll are faster than programs produced by a heuristic, classical version of our compiler and comparable to highly optimized, expert-written programs.

Despite its potential, synthesis has not been used in main-stream compilers because of its scability issues and lack of a development tool for synthesis-aided compilers. In the domain of classical compilers, researchers have developed design patterns and frameworks that accelerate the development of classical compilers [54, 89, 163]. These frameworks provide well-developed analyses, transformations, and heuristics that are adaptable to new, but

Figure 1.3: Decomposition of the Chlorophyll compiler. Synthesis components are highlighted in blue.

still conventional, architectures. In this thesis, I introduce the analogue of these reusable components for synthesis-aided compilers and offer similar frameworks to developers. From my experience with Chlorophyll and Floem, program synthesis and resource allocation synthesis are important building blocks for synthesis-aided compilers. As part of these frameworks, I also tackle the scability challenge and present techniques that make synthesis more scalable.

### **Program Synthesis**

I believe that program synthesis — which searches for an optimal program equivalent to a specification program — can be used to sidestep the development of difficult transformations. This technique has been used to optimize both high-level programs [21, 42, 147] and low-level machine code [19, 103, 136], but it is often used as a standalone tool separate from a compiler's workflow. In Chlorophyll, I demonstrate that it is feasible to use a superoptimizer (the last component in Figure 1.3) as a part of the compiler.

As an effort toward building a development tool for synthesis-aided compilers, I develop **GreenThumb (Chapter 4)**, a framework for building a superoptimizer for any Instruction Set Architecture (ISA). To address the scalability problem, I implement Lens, an enumerative search algorithm that can optimize small- to medium-size program fragments faster than existing techniques. To optimize larger program fragments, I introduce a context-aware window decomposition, optimizing a fragment of the entire code with the precise precondition

and postcondition from the surrounding context. Lastly, I compensate for the limitation of an enumerative search by combining symbolic and stochastic search into the system. To make superoptimization even more practical, we can cache superoptimized code to avoid an expensive search when optimizing programs we have seen before.

I use Greenthumb to build superoptimizers for GA144, ARM, and a subset of LLVM. The ARM superoptimizer synthesizes code fragments that are up to 82% faster than code generated by gcc -03 on realistic benchmarks. Linki Tools — a startup that helps customers develop toolchains for programming various embedded systems — create S10 superoptimization framework based on Greenthumb. The initial prototype of S10 is built upon Greenthumb and has been refactored into a commercial product that supports multiple variations of RISC-V ISAs.

### Resource Allocation Synthesis

Second, I envision that resource allocation synthesis — which searches for an optimal solution that satisfies hard resource constraints — can be used to sidestep the development of complicated algorithms to solve complex resource allocation problems. Prior work has used synthesis (as known as constraint solving in the compiler literature) to perform optimal register allocation [14, 59], instruction scheduling [93, 168], instruction selection [22, 169], high-level synthesis [87], partitioning [114], and layout and routing [170]. However, it remains difficult to encode a resource allocation problem into constraints that can be solved efficiently. In Chlorophyll, I demonstrate that program partitioning (the first component in Figure 1.3) can be formulated as a type inference problem, which can be easily encoded into SMT formulas by implementing a type checker in Rosette [159, 160]. This approach eases the development of the partitioning synthesizer by utilizing Rosette to automatically generating SMT formulas through symbolic evaluation.

Later, I develop a **resource-mapping library** (Chapter 5), a prototype toward a retargettable resource allocation mapping framework. Using this library, users can simply implement a function that calculates the cost of a given candidate and use assertion constructs to specify hard constraints such as memory capacity constraints. The framework then automatically generates integer linear programming (ILP) constraints, which can be solved more efficiently than does SMT, for resource allocation problems [80, 114, 116, 168]. I modify the partition type checker in Chlorophyll to use this library, which reduces its search time by more than a few orders of magnitude.

### 1.6 Summary of Contributions

In summary, this thesis makes the following contributions:

- Chlorophyll (Chapter 2), the first synthesis-aided compiler that applies both program synthesis and resource allocation synthesis as parts of the main workflow of the compilation process. It provides a programming model that allows programmers to design parts of the high-level program partitioning and layout, and leave low-level details for the compiler to fill in.

- FLOEM (Chapter 3), a programming system for developing network applications in a combined CPU-NIC environment. Its programming abstractions allow programmers to precisely specify offloading strategies and let the system infer what data need to be transferred and handle low-level communication details between CPU and NIC.

- Greenthumb (Chapter 4), a superoptimizer construction framework that tackles the scalability and retargettability challenges of superoptimization. It is equipped with a new scalable superoptimization algorithm and designed to be extensible to new ISAs. The Linki Tools company has developed commercial superoptimization framework, S10 [99], from the resurgence of GreenThumb. The company used S10 to build superoptimizers for many variants of RISC-V and is in the process of developing superoptimizers for x86 and ARM.

- The resource-mapping library (Chapter 5), a prototype toward a scalable, retargettable resource allocation synthesis that tackles the challenge of formulating resource mapping problems into efficient constraints.

### Chapter 2

# Chlorophyll: Programming Spatial Architectures

Energy requirements have been dictating simpler processor implementations with more energy dedicated to computation and less to processor control. Simplicity is already the norm in low-power systems, where 32-bit ARM dominates the phone computer class [155]; the 16-bit TI 430MSP is a typical example of a low-power embedded controller; the even simpler 8-bit Atmel AVR controller powers Arduino [15, 109].

The GreenArrays GA144 is a recent example of a low-power minimalistic spatial processor<sup>1</sup>, composed of many small, simple, identical cores [64]. Likely the most energy-efficient commercially available processor, it consumes 9-times less energy and runs 11-times faster than the TI MSP430 low-power microcontroller on a finite impulse response benchmark [17]. Naturally, energy efficiency comes at the cost of low programmability; among the many challenges of programming the GA144, programs must be meticulously partitioned and laid out onto the physical cores.

We imagine that future low-power processors will likely be similar to the GA144. First, they will likely be spatial with simple interconnects between resources or cores. Second, they will likely have radically different ISAs from what we commonly use today. Third, they will likely be minimalistic, providing little programmability support and therefore placing a greater burden on programmers and compilers.

Materials in this chapter are based on work published as (1) Phothilimthana et al., "Chlorophyll: Synthesis-Aided Compiler for Low-Power Spatial Architectures," in proceedings of PLDI 2014 [121] and (2) Phothilimthana et al., "Compiling a Gesture Recognition Application for a Low-Power Spatial Architecture," in proceedings of LCTES 2016 [123].

<sup>&</sup>lt;sup>1</sup>A spatial architecture is an architecture for which the user or the compiler must assign data, computations, and communication primitives explicitly to its specific hardware resources such as computing units, storage, and an interconnect network.

### 2.1 Contributions and Rationale

In this chapter, we introduce a new programming model and a synthesis-based compiler for such spatial processors. Our primary hardware target is the GA144 which takes these design features — spatiality, idiosyncrasy of ISA, and minimalism — to extremes, maximizing the demands on our programming tool chain; if we can build a synthesizer for this processor, we should be able to build ones for other low-power sptial processors as well.

Our programming model allows programmers to selectively partition key data structures and code, leaving the remaining partitioning and communication code generation to synthesizers. In particular, we design the programming model with a specific division of responsibilities as follows.

### A programmer is responsible for:

- Partial program partitioning and layout. Programmers sometimes prefer to control how data structures and code should be layouted but not to deal with the low-level details of the resulting communication code.

- Control-flow statement replication. Although this decision may not need human's insight, without a programmer's guidance, the compiler will have to deal with a very complicated cost model. Therefore, we delegate this task to the programmer.

- Parallelism. We do not support automatic parallelization because of conflicting goals. The compiler has to choose between minimizing for latency (consequently, obtaining parallelism) and resource usage (consequently, minimizing power consumption). These are conflicting goals because parallelism on GA144 requires more cores and memory. We believe that this kind of decision should be made by the programmer and not by the compiler.

### Synthesizers are responsible for:

- The rest of program partitioning, layout, and routing. This is because heuristics often fail to find optional solutions, and developing a good heuristic algorithm to solve this task is difficult.

- Instruction-level optimization. GA is a stack-based ISA, and there is no well-known optimization passes developed for stack-based instructions, so we delegate this task to a synthesizer to automatically discover optimizations.

Classical transformations are responsible for tasks that can be solved by simple transformations:

- Code separation from a single program into 144 per-core programs.

- IR-to-assembly transformation (with no optimization).

### 2.2 Overview

CHLOROPHYLL compiles a high-level program to spatial machine code via synthesis. However, solving large and complex problems with synthesis is infeasible. We demonstrate that the compilation problem can be decomposed into partitioning, layout and routing, code separation, and code generation, as depicted in Figure 1.3. Most of these subproblems are difficult for classical compilers but can be solved naturally using synthesis techniques.

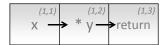

**Step 1 (partition)** The input to this step is a source program with *partition annotations* which specify the logical core (partition) where code and data reside. The annotations allow the programmer to provide insight about the partitioning or experiment with different partitioning just by changing the annotations. An input program does not have to be fully annotated. For example, in this program

```

int@0 mult(int x, int y) { return x * y; }

```

we specify that the result will be delivered at partition 0 but do not specify the partitions of variable x, y, and operation +.

The compiler then infers (i.e., synthesizes) the rest of the partition annotations such that each program fragment (per-core program) fits into a core, minimizing a static over-approximation of the amount of messages between partitions. Here is one possible mapping (for a very tiny core):

```

int@0 mult(int@2 x, int@1 y) { return (x!1 *@1 y)!0; }

```

The inferred annotations indicate that when function  $\operatorname{mult}$  is called, x is passed as an argument at partition 2 and y is passed as another argument at partition 1. ! is a send operation. The program body's annotations specify that the value of x at partition 2 is sent to partition 1, and is multiplied with the value of y. Finally, the result of the addition is sent to partition 0 as the function's return value.

Step 2 (layout) The layout synthesizer maps program fragments onto physical cores, minimizing a refined approximation of communication costs. It also determines a communication path (routing) between each pair of cores. We map this synthesis problem to an instance of the well-known Quadratic Assignment Problem (QAP) which can be solved exactly or approximately [90, 46, 51, 145]. We chose to use the Simulated Annealing algorithm as it is one of the fastest techniques and produces a nearly optimal solution [46]. Given the partitioned mult function from the previous step, the figure below shows the result of this step.

**Step 3 (code separation)** The separator splits the fully partitioned program into percore program fragments, inserting sends and receives for communication. This step uses a classical program transformation. We guarantee that the resulting separated programs are deadlock-free by disallowing instruction reordering within each core. Our running example results in these program fragments:

```

// core(1,1) core ID is (x,y) position on the chip

void mult(int x) { send(EAST, x); }

// core(1,2)

void mult(int y) { send(EAST, read(WEST) * y); }

// core(1,3)

int mult() { return read(WEST); }

```

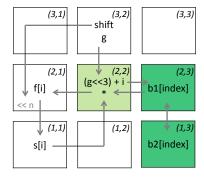

Step 4 (code generation) The code generator first naively compiles each program fragment into machine code (arrayForth, a stack-based assembly for GA144). The code is then optimized with a superoptimizing synthesizer, which searches the space of possible instruction sequences to find ones that are correct and fastest [103]. Although the superoptimizer is allowed to reorder evaluations, it preserves the order of sends and receives which is sufficient to prevent deadlock. We apply a sliding window technique to the synthesizer to adaptively merge small code sequences into bigger ones and input it back into the synthesizer. The synthesizer persistently caches synthesized code to avoided unnecessary recomputation.

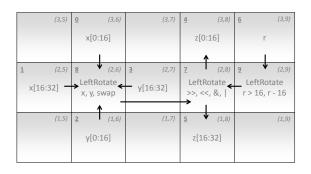

Figure 2.1 illustrates these four steps with a larger example, LeftRotate program. Figure 2.1(b) shows the result after partitioning the program in Figure 2.1(a) with 64 words of memory per core. The layout and routing of the program is shown in Figure 2.1(c) after the layout step, and Figure 2.1(d) displays the program at core (2,6) after the code separation step.

### 2.3 Programming Model for Partitioning

In a very limited-resource environment such as a very small many-core, distributed-memory processor, a program partitioning strategy is very critical because it not only affects the performance of the application but, more importantly, determines whether the application can fit and run on the processor. In this section, we present programming abstractions to control mapping of data and code to different partitions, as well as replication of program control flow constructs (i.e., program structures). These abstractions simplify reasoning about partitioning and obviate the need for explicit communication code. We achieve these goals by:

- extending a simple type system with a *partition type* and optimally inferring unspecified partitions, and

- introducing a language construct to control the replication of control statements, trading communication efficiency for code size reduction.

```

int leftrotate(int x, int y, int r) {

1

2

if(r > 16) {

3

int swap = x;

x = y;

4

y = swap;

6

r = r - 16;

7

8

return ((y >> (16 - r)) | (x << r)) & 65535;

9

}

10

11

void main() {

12

int@{[0:32]=0,[32:64]=1} x[64];

int@{[0:32]=2,[32:64]=3} y[64];

13

14

int@{[0:32]=4,[32:64]=5} z[64];

15

// x[0] to x[31] live at partition 0,

// x[32] to x[63] live at partition 1, and so on.

16

17

int@6 r = 0;

18

for (i from 0 to 64) {

19

20

z[i] = leftrotate(x[i],y[i],r) -@place(z[i]) 1;

21

r = r + \theta place(r) 1; // + happens at where r is

22

if (r > 32) r = 0;

23

}

}

24

```

(a) Input source code written in Chlorophyll

(c) Output from layout synthesizer. Numbers at the top-left corners represent partition IDs corresponding to the partition annotations in the source code. Numbers at the top-right corners are physical core coordinates.

(b) Output from partitioner when memory is 64 words

(d) Program at core (2,6) after code separation

Figure 2.1: Example program written in Chlorophyll, and intermediate results from partitioning, layout, and code separation steps

### Partition Annotation

CHLOROPHYLL syntax is a subset of C with some modifications and partition annotation, specifying the partitions of data and operations. Programmers must be able to use partition annotations to:

- (1) place data and operations to specific cores

- (2) constrain some data and operations to be on the same core

- (3) distribute an array onto multiple cores, and

- (4) replicate some operations on multiple cores to process data in parallel.

Following these requirements, we design partition annotations (A) to be expressed as follows:

```

\begin{array}{rcl} A & := & N \mid \{range = N, \ldots\} \mid \mathsf{place}(var) \mid \mathsf{place}(array) \\ range & := & [N:N] \\ N & := & \mathsf{natural\ number} \\ var & := & \mathsf{variable} \\ array & := & \mathsf{array\ access} \end{array}

```

For (1), to place data or an operation to a specific partition (logical core), programmers annotate a variable or an operation with place(l). Programmers can then map a logical core l to a physical core p as explained later in this section. We do not want l in place(l) to control the mapping to a physical core directly because we do not want the programmers to reason about the chip's layout and data routing when they want to partition programs only at the logical cores level.

For (2), to constrain a variable or an operation y to be at the same core as another variable x, programmers annotate y with place(x).

For (3), to distribute an array x onto multiple cores, programmers annotate x with  $\{[n_0:n_1]=l_0,[n_1:n_2]=l_1,...\}$ . The annotation will put x[i] on logical core  $l_k$ , when  $n_k \leq i < n_{k+1}$ .

For (4), to replicate an operation on multiple cores to process a distributed array x in parallel, programmers annotate the operation with place(x[i]), where i is a loop variable. place(x[i]) refers to the partition where the ith entry of array x lives. Note that place(x[i]) can only be used inside the body of a for loop with an iterator i.

**Example.** Figure 2.1(a) shows LeftRotate program implemented in Chlorophyll.

- On line 18, we set the partition of variable r to be 6 by annotating its declaration.

- On line 21, we annotate + with place(r) to execute + on the same partition as r.

- On line 12, we assign the partitions of distributed array x such that for  $0 \le i < 32$ , x[i] lives in partition 0, and the rest in partition 1.

- On line 21, operation + is assigned to partition 6.

- On line 20, operation is assigned to place(z[i]); when  $0 \le i < 32$ , operation at partition 4 is executed, and when  $32 \le i < 64$ , operation at partition 5 is executed. The loop on line 19 is a loop with a statically-known bound of the form for (i from e1 to e2) {...}, where e1 and e2 are constants. The iterator i starts from e1 and is incremented by 1, and the loop condition is i < e2.

Note that most of the data and operations in the program are left unannotated. Their partitions will be automatically inferred by the partitioning synthesizer to minimize communication between cores. Hence, Chlorophyll allows the programmers to specify data and operation when they have a rough partitioning plan in mind, and to leave some unannotated when they want the compiler to decide.

Our partition annotations resemble data distribution annotations from many high performance computing languages [28, 37, 107, 112, 173]. While a scalar variable is replicated on all processors in these languages, a scalar variable lives in only one place in Chlorophyll because of our highly-restricted space requirement; same for an operator. Our space requirement is a major factor that distinguishes our language design from prior high-performance parallel languages.

### Language Constructs

Constants, variables, arrays, operators, and statements all occupy space in memory. Most programming constructs — such as variable declarations, variable accesses, variable assignments and binary operations — occupy a constant amount of memory in one partition, so we can estimate the space occupied by the program with a simple lookup table. However, we have to handle control flow constructs and arrays with more care as they may require more complex communication between the involved partitions.

### Arrays

There are two kinds of arrays:

- **Non-distributed arrays** only live in one partition. An index into this type of array has to live at the same partition as the array itself.

- **Distributed arrays** live in multiple partitions. Arrays x, y and z from LeftRotate are examples. This type of array can only be indexed by affine expressions of surrounding loop variables and constants. Accessing this type of array requires no communication because the indexes are comprised of loop variables, which live in every body partition. Chlorophyll currently does not support other kinds of indexing into distributed arrays.

A distributed array can be declared in two ways. First, the distributed array x in LeftRotate in Figure 2.1 is declared as:

```

int@{[0:32]=0,[32:64]=1} x[64];

```

Alternatively, it can be declared using the following syntax:

```

int[blocksize]@{p_1,p_2,...,p_n} array[N];

```

where n = ceil(N/blocksize). With the second syntax, the same distributed array x can be declared as:

```

int[32]@{0,1} x[64];

```

### Control Flow Constructs

CHLOROPHYLL provides a construct for programmers to control the replication of control statements, trading communication efficiency for code size reduction. We first describe the two extreme strategies: the *actor model*, which replicates no code, and the *SPMD model*, which replicates all control statements. We then describe the construct to control the replication.

### SPMD vs. Actor Partitioning Strategy

An invariant of our partitioning is that data and non-control computations are not replicated; they are always assigned to exactly one logical partition, which is mapped to one physical core. The programmer controls only replication of control statements (ifs and loops), which determine the control condition, i.e., when a statement is executed.